INTRO

Vol.230

완벽한 반도체를 위한

끝없는 노력

반도체를 만들기 위한 공정은 크게 전공정과 후공정으로 나눌 수 있다.

전공정은 웨이퍼를 제조하고 회로를 새기는 과정이고, 후공정은 칩을 패키징하는 과정이다.

반도체 후공정은 반도체 첨단 선단의 문제를 기술적으로 해결하는 해법을 제시하는 것으로 여겨지기 때문에

계속해서 개발되어야 할 중요한 부분이 됐다.

섬세한 반도체, 보호가 필요하다

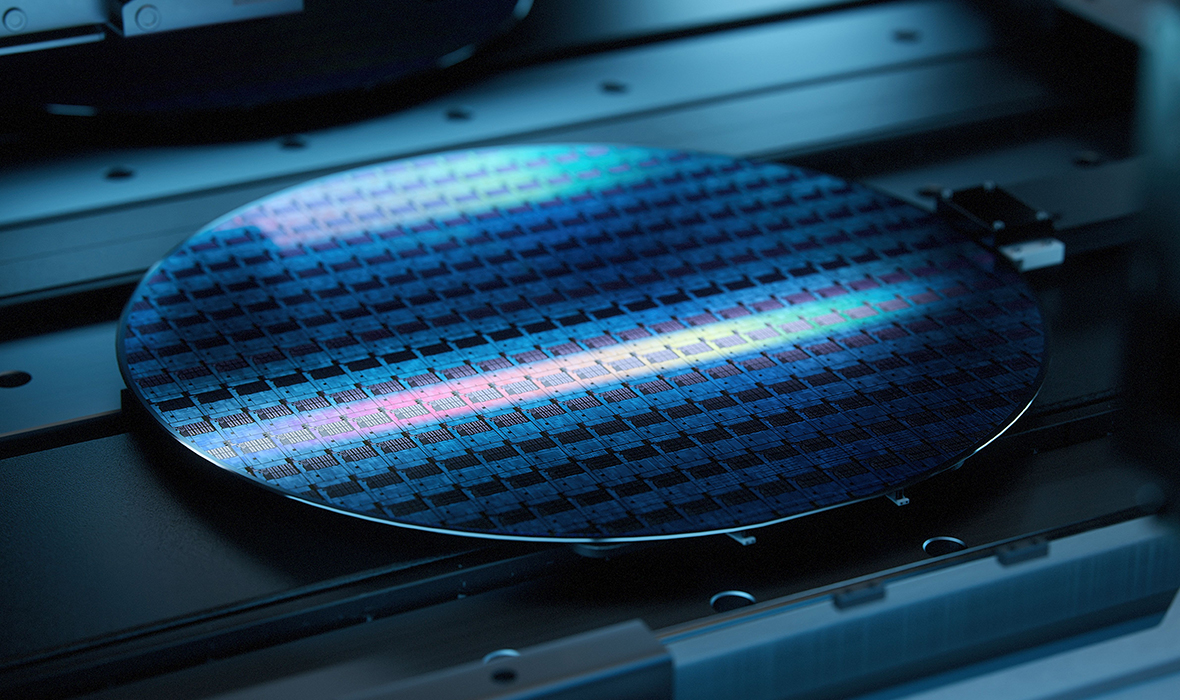

웨이퍼 기판의 모습. 이 위에 다양한 반도체 칩이 장착된다.

반도체 칩은 수많은 웨이퍼 공정을 통해 뛰어난 메모리, 로직 기능이 있다 하더라도 그 자체로 사용될 수 없다. 깨지기 쉬운 실리콘 소재로 만들어졌기 때문이다. 또한 웨이퍼 공정으로 만들어진 반도체는 기계적, 화학적 충격에도 취약하다. 그래서 반도체 칩을 보호할 공정인 패키징이 필요하다.

반도체 패키징은 단어 자체의 의미를 생각하면 쉽다. 반도체를 포장하여 외부로부터 안전하게 보호하는 것이다. 반도체 칩을 탑재시킬 기기에 알맞은 형태로 포장하는 것이 반도체 패키징이다.

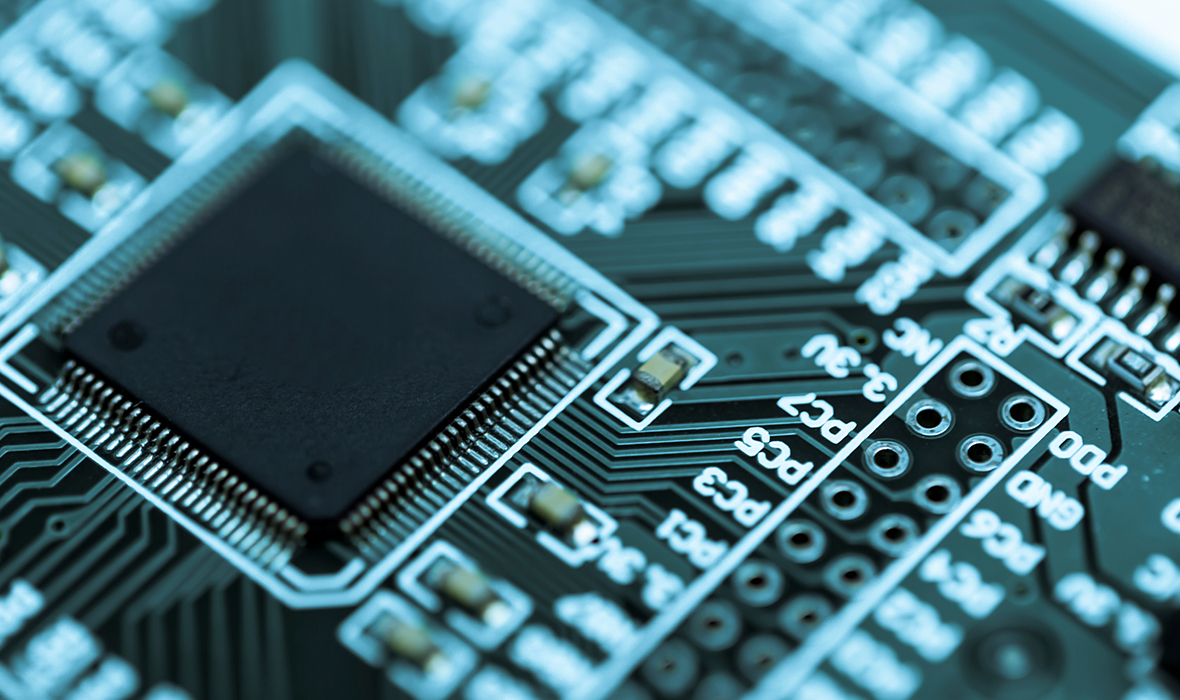

반도체 패키징은 반도체를 보호하는 역할 이외 3가지 주요한 역할이 있다. 먼저는 전기적 연결(Electrical Connection)이다. 이는 반도체 칩과 기기를 전기적으로 연결하는 역할이다. 이를 통해 반도체에 필요한 전력을 공급하고, 원하는 기능을 수행할 수 있는 신호를 입·출력할 수 있게 된다.

두 번째는 열 분산(Heat Dissipation)이다. 반도체 칩은 동작할 때 열이 발생한다. 이때 반도체 패키지는 반도체 칩을 둘러싸고 있는데, 반도체 칩으로부터 발생한 열을 패키지가 발산시켜 주는 역할을 하는 것이다.

세 번째는 기계적 연결(Mechanical Connection)이다. 이는 문자 그대로이다. 반도체 칩이 작동할 수 있도록 기기에 잘 부착될 수 있게 연결하는 역할이다.

반도체 패키지, 계속되는 발전

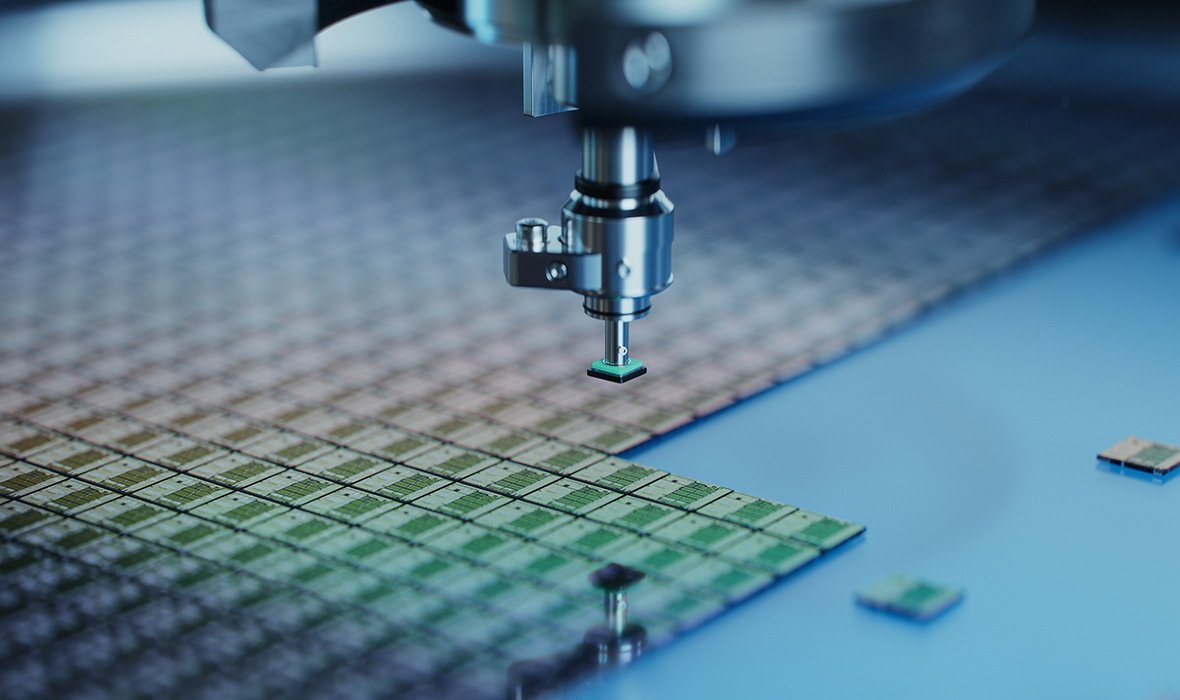

0차 레벨 패키징의 모습

반도체 패키징의 과정은 0차 레벨 패키징부터 3차 레벨 패키징으로 구분시킬 수 있다. 0차 레벨 패키징은 실리콘 웨이퍼에서 반도체 칩을 잘라내는 과정이다. 이를 분리하여 패키지 기판에 연결하는 것을 1차 레벨 패키징이라 하고 패키징으로 단품화 하여 모듈의 형태로 만드는 것을 2차 레벨 패키징이라 한다. 이렇게 제작된 모듈을 카드나 보드(Board)에 장착한 후 시스템 보드에 장착하는데, 이 과정을 3차 레벨 패키징이라 부른다.

반도체 패키징에서 중요한 것은 패키징의 주요한 역할들을 완벽하게 수행하는 것이다. 이를 위한 반도체 패키징 기술은 계속해서 발전하고 있다. 반도체 칩의 속도를 구현할 수 있도록 돕는 플립 칩(Flip Chip) 패키징 기술, 실리콘 관통 전극(TSV)을 이용한 패키징 기술 등이 개발되었다. 또한 기존 한 패키징 안에 하나의 반도체 칩만을 넣을 수 있던 구조에서 벗어난 반도체 적층 기술도 발전 중이다. MCP(Multichip Package), SiP(System In Package) 기술은 한 패키징에 여러 개의 칩을 적층시킬 수 있다.

이외에도 남극, 열대우림, 우주까지 다양한 환경에도 반도체를 안정적으로 사용할 수 있도록 보호 기능을 높이는 신뢰성 높은 패키징 기술(Reliability), 반도체의 열 방출 효율을 높일 열전도도*가 좋은 신소재를 개발하는 등의 노력이 계속되고 있다.

* 열전도도: 물체가 열을 전달하는 능력의 척도를 말한다.

또한 중요한 이슈로 떠오른 것은 바로 첨단 반도체 패키징이다. 기술의 발달로 하나의 웨이퍼에 제작할 수 있는 반도체 칩의 수가 많아지면서 동시에 크기는 작아졌다. 이 작아진 반도체 칩의 기능을 온전히 발휘할 수 있게 패키징의 공정 기술도 최적화가 필요해진 것이다. 이를 위해 Fan-Out 패키징, 2.5D 패키징, 칩렛 패키징 기술 등이 활발하게 개발되고 있다. Fan-Out 패키징은 매우 얇은 재배선층에 패키징 하는 기술이고, 2.5D 패키징은 실리콘 인터포저를 적용한 패키징 기술이며, 칩렛 패키징은 서로 다른 기능을 하는 다수의 조각 칩을 첨단 패키징 기판에 집적하는 기술이다.

뛰어난 반도체의 기능이 제대로 발휘되기 위해선 그에 맞는 패키징 기술이 뒷받침되어야 한다. 다양한 기능을 지니고, 다수의 반도체 적층이 가능한 최적의 패키징 기술 개발을 위한 전 세계적인 관심이 쏠리는 추세다.